# Agilent E2929A/B Opt. 300 PCI-X Exerciser

## User's Guide

Agilent Technologies

#### **Important Notice**

All information in this document is valid for both Agilent E2929A and Agilent E2929B testcards.

#### Copyright

© 2000, 2001 Agilent Technologies. All rights reserved.

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies Inc. as governed by United States and international copyright laws.

Author: Anja Schauer, t3 medien GmbH

#### Notice

The material contained in this document is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

## Contents

| Documentation O   | verview                                               | 7  |

|-------------------|-------------------------------------------------------|----|

| PCI-X Exerciser C | lverview                                              | ç  |

|                   | Gaining an Active Part in Optimization and Validation | 10 |

|                   | PCI-X Exerciser Architecture                          | 12 |

|                   | PCI-X Exerciser Configurations                        | 15 |

|                   | Setting Up a PCI-X Exerciser Test                     | 17 |

|                   | Typical PCI-X Transactions                            | 17 |

| Running A Sample  | e PCI-X Exerciser Session                             | 19 |

|                   | Example Scenarios                                     | 20 |

|                   | Preparing for the Exerciser Guided Tour               | 21 |

|                   | Guided Tour: Generating Requester-Initiator Block     |    |

|                   | Transfer                                              | 23 |

|                   | Loading the Setup Files                               | 23 |

|                   | Setting up a Requester-Initiator Transaction          | 24 |

|                   | Running the Test                                      | 25 |

|                   | Viewing the Results                                   | 26 |

|                   | Guided Tour: Specifying Requester-Initiator Behavior  | 29 |

|                   | Loading the Setup Files                               | 30 |

|                   | Setting up the Requester-Initiator Behaviors          | 30 |

|                   | Running the Test                                      | 31 |

|                   | Viewing the Results                                   | 32 |

|                   | Guided Tour: Specifying Completer-Target Behavior     | 34 |

|                   | Loading the Setup Files                               | 35 |

|                   | Setting up the Target Decoders                        | 36 |

|                   | Specifying the Completer-Target Protocol Behavior     | 37 |

|                   | Viewing the Results                                   | 38 |

| Split Response       40         Starting the Command Line Interface       40         Entering the Required CLI Commands       41         Guided Tour: Specifying Completer-Initiator Behavior       43         Loading the Setup Files       44                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Entering the Required CLI Commands 41<br>Guided Tour: Specifying Completer-Initiator Behavior 43                                                                                                                                                                                                                                                                        |

| Guided Tour: Specifying Completer-Initiator Behavior 43                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                         |

| Loading the Setup Files 44                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                         |

| Setting up the Completer-Initiator Behaviors 44                                                                                                                                                                                                                                                                                                                         |

| Running the Test 44                                                                                                                                                                                                                                                                                                                                                     |

| Viewing the Results 45                                                                                                                                                                                                                                                                                                                                                  |

| Guided Tour: Specifying Requester-Target Behavior 46                                                                                                                                                                                                                                                                                                                    |

| Loading the Setup Files 47                                                                                                                                                                                                                                                                                                                                              |

| Setting up the Requester-Target Decoder 48                                                                                                                                                                                                                                                                                                                              |

| Specifying the Requester-Target Protocol Behavior 49                                                                                                                                                                                                                                                                                                                    |

| Viewing the Results 50                                                                                                                                                                                                                                                                                                                                                  |

| The PCI-X Exerciser as a Requester-Initiator Device 53                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                         |

| Programming Requester-Initiator Transactions 54                                                                                                                                                                                                                                                                                                                         |

| Programming Requester-Initiator Transactions 54<br>Requester-Initiator Transactions Overview 55                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                         |

| Requester-Initiator Transactions Overview 55                                                                                                                                                                                                                                                                                                                            |

| Requester-Initiator Transactions Overview55Available Transaction Properties59                                                                                                                                                                                                                                                                                           |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Inititator Transactions62                                                                                                                                                                                                                                         |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Initiator Transactions62Programming the Requester-Initiator Behaviors63                                                                                                                                                                                           |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Initiator Transactions62Programming the Requester-Initiator Behaviors63Available Requester-Initiator Behaviors64                                                                                                                                                  |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Initiator Transactions62Programming the Requester-Initiator Behaviors63Available Requester-Initiator Behaviors64Latencies between Requester-Initiator Transactions65                                                                                              |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Initiator Transactions62Programming the Requester-Initiator Behaviors63Available Requester-Initiator Behaviors64Latencies between Requester-Initiator Transactions65Starting the Requester-Initiator66                                                            |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Initiator Transactions62Programming the Requester-Initiator Behaviors63Available Requester-Initiator Behaviors64Latencies between Requester-Initiator Transactions65Starting the Requester-Initiator66Preparing Test Execution66                                  |

| Requester-Initiator Transactions Overview55Available Transaction Properties59How to Specify Requester-Initiator Transactions62Programming the Requester-Initiator Behaviors63Available Requester-Initiator Behaviors64Latencies between Requester-Initiator Transactions65Starting the Requester-Initiator66Preparing Test Execution66Running the Requester-Initiator68 |

| The PCI-X Exercise | er as a Completer-Target Device                  | 73         |

|--------------------|--------------------------------------------------|------------|

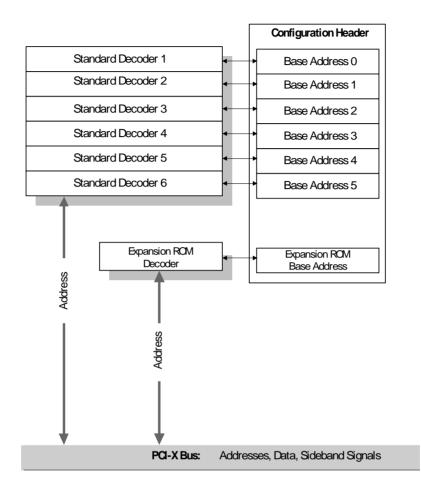

| (                  | Configuration Space and Completer-Target Decoder | S 74       |

|                    | Configuration Space Header                       | 75         |

|                    | Target Decoder Properties                        | 77         |

|                    | Data Resources                                   | 81         |

| T                  | Farget Decoder Setup                             | 82         |

|                    | Programming the Completer-Target Decoders        | 83         |

|                    | Modifying the Configuration Space Header         | 85         |

|                    | Overwriting BIOS Settings                        | 88         |

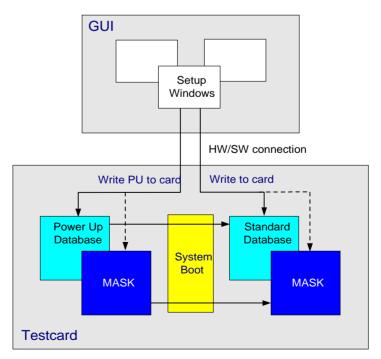

| S                  | Standard and Power-Up Databases                  | 89         |

| F                  | Programming Completer-Target Behaviors           | <b>9</b> 1 |

| Ļ                  | Available Completer-Target Behaviors             | 92         |

|                    | Initial Latencies                                | 93         |

|                    | Defining a Split Response Condition              | 94         |

| The PCI-X Exercise | er as Completer-Initiator Device                 | 95         |

| F                  | Programming Completer-Initiator Behaviors        | 90         |

| Ļ                  | Available Completer-Initiator Behaviors          | 97         |

|                    | Defining Split Completion Messages               | 99         |

| (                  | Generating Split Completion Transactions         | 100        |

| The PCI-X Exercise | er as a Requester-Target Device                  | 101        |

| F                  | Requester-Target Decoder Setup                   | 102        |

| F                  | Programming Requester-Target Behaviors           | 103        |

|                    | Available Requester-Target Behaviors             | 104        |

| Using Data Resour  | ces                                              | 107        |

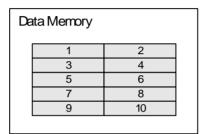

| [                  | Data Memory                                      | 107        |

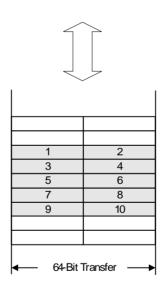

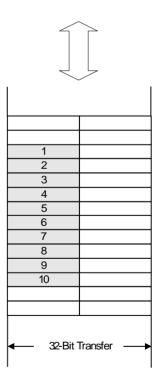

|                    | Data Memory Organization                         | 108        |

|                    | How to Use the Data Memory Editor                | 110        |

| Γ                  | Data Generator                                   | 112        |

|                    | Performing Unidirectional Data Path Verification | 11:        |

|                    | How to Use the Data Generator                    | 114        |

| F                  | Real-Time Data Compare                           | 116        |

| F                  | Programmable Data Path Configurations            | 117        |

|                    |                                                  |            |

| Generating Interrupts                  |     |

|----------------------------------------|-----|

| Interrupt Capabilities of the Testcard | 120 |

| Asserting and Deasserting Interrupts   | 121 |

| Using the Command Line Interface       | 123 |

| How to Start the CLI                   | 124 |

| Basic CLI Command Syntax               | 125 |

| Using CLI Scripts                      | 126 |

# **Documentation Overview**

This section shows you the different types of documents offered by Agilent Technologies and gives you an overview of which documents are available when you work with the Agilent E2929A/B PCI-X Exerciser and Analyzer.

All documents are valid for both Agilent E2929A and Agilent E2929B testcards. The following documents are available:

#### Getting Started Guide • Getting Started Guide

Introduces standard analysis features and provides an example of how to set up the protocol observer.

This guide also gives detailed information about the hardware and interfaces.

#### User's Guides • Agilent E2929A/B Opt. 300 PCI-X Exerciser User's Guide

Provides information on programming the testcard as an initiator and/or target device. It shows you how to actively stimulate the PCI-X bus.

This guide shows how to:

- Initiate data transfers on the PCI-X bus (act as requester-initiator).

- Act as completer-target.

- Handle split completion transactions (act as completer-initiator).

- Handle open requests (act as requester-target).

- Agilent E2929A/B Opt. 100 PCI-X Analyzer User's Guide

Provides information on how to examine the behavior of a PCI-X device on the bus and shows how to perform functional tests such as data compares.

• Agilent E2929A/B Opt. 200 PCI-X Performance Optimizer User's Guide

Provides all features that are needed to evaluate and optimize any device under test in terms of the performance.

#### GUI and C-API/PPR References • Agilent E2929A/B Windows and Dialog Boxes Reference

Provides reference information on all windows and dialog boxes of the Agilent E2920 graphical user interface (GUI).

• Agilent E2929A/B Opt. 320 C-API/PPR Reference

Describes all C functions, types and definitions of the application programming interface of the Agilent E2929A/B PCI-X testcard.

This reference also provides the commands and abbreviations that are used in the command line interface (CLI) of the graphical user interface.

# **PCI-X Exerciser Overview**

Agilent Technologies' E2920 Verification Tools, PCI-X Series is your "window into the system" during product development, giving you access to almost all of the system components located on the PCI-X bus, as well as devices and adapters on secondary buses or within the system.

The PCI-X Exerciser (option #300) allows you to overcome the passive role of monitoring the PCI-X bus. With the PCI-X Exerciser, the testcard can be programmed to behave as a requester-initiator, a completertarget, a completer-initiator and/or requester-target device to generate any kind of traffic on the bus.

"Gaining an Active Part in Optimization and Validation" on page 10 gives an overview of how you can use the Exerciser during the various phases of the design cycle.

"PCI-X Exerciser Architecture" on page 12 introduces the structure of the PCI-X Exerciser and shows the interaction of single components.

*"PCI-X Exerciser Configurations" on page 15* shows examples of possible configurations for PCI-X Exerciser tests.

*"Setting Up a PCI-X Exerciser Test" on page 17* outlines the major setup steps that are required.

In most tests, the Exerciser will act as a initiator device and/or a target device on the PCI-X bus, initiating or serving transactions respectively. *"Typical PCI-X Transactions" on page 17* introduces in this basic term.

# Gaining an Active Part in Optimization and Validation

The Agilent Technologies PCI-X Exerciser's focus in the design cycle clearly lies on those phases, when you are optimizing and validating your PCI-X design for reliability.

**Optimization Phase** The Exerciser is designed to enable you to optimize your PCI-X design for reliability.

The Exerciser plays an active role in the analysis of complex PCI-X scenarios by letting you set up worst-case test patterns quickly. It provides the full flexibility to set up all the test scenarios you need, with your own choice of protocol and traffic variations, wait states, retries and disconnects, latencies, and burst sizes. You can also control the use of memory as well as of read and write commands, which which is especially important when testing the correct functioning of bridge devices.

This not only saves you the tedious chore of having to test your device with various other PCI-X components one after the other, but also allows you to test in a repeatable way, which means that you can reproduce any errors for deeper investigation. You can also run functional tests, directing the Exerciser to generate and transmit large blocks of data in specified time intervals, thus testing how much PCI-X traffic your device can handle.

Validation Phase Validating your PCI-X device means ensuring its long-term reliability. This means ensuring that it remains stable under any application conditions, with any combination of plug-ins and any kind of traffic on the bus.

> Using the PCI-X Exerciser as an initiator or a target device, you can test your design repeatedly and consistently from the earliest opportunity, from the earliest stages during bring-up and integration, before a complete system is available..

In combination with the C-API/PPR options, the Exerciser offers fully controllable system-test, with wide coverage, reproducibility, and rootcause-analysis capabilities that will reveal system-critical problems faster than any hot mock-up testing could.

# **PCI-X Exerciser Architecture**

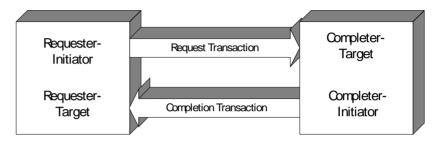

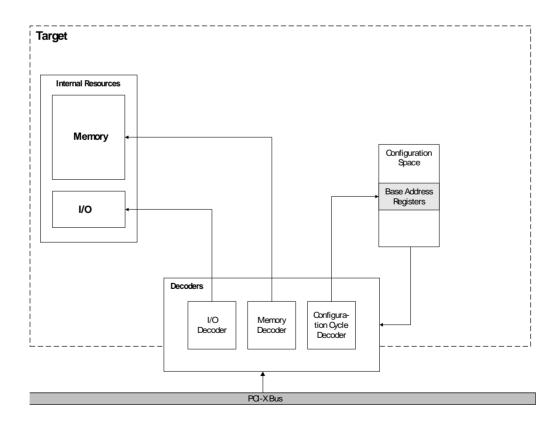

The Agilent E2929A/B testcard can act as an initiator or a target device on the PCI-X bus to generate any kind of PCI-X transfer.

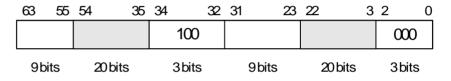

Because PCI-X allows you to perform split transactions, initiator and target have been subdivided. This is shown in the following figure:

The **requester-initiator (RI)** is the initiator of a transaction. It initiates all transactions except split completion transactions.

The **completer-initiator (CI)** initiates split completion transactions only.

The **completer-target (CT)** is the target for a transaction. It decodes all transactions except split completion transactions.

The requester-target (RT) decodes split transactions only.

#### **PCI-X Exerciser Architecture Overview**

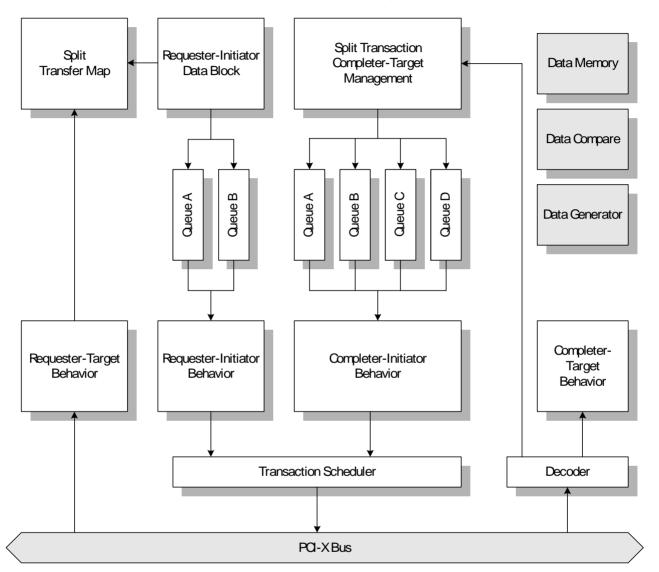

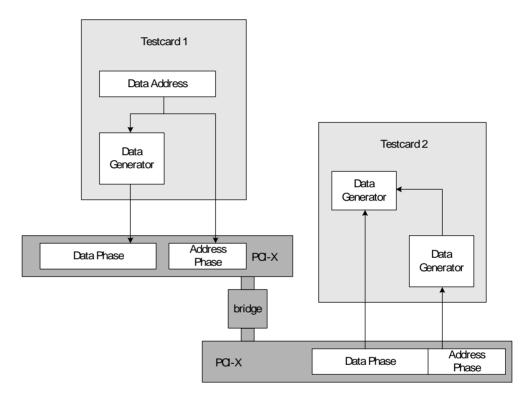

The following figure shows the architecture of the PCI-X Exerciser and the connections between single components:

The exerciser is based on the following concepts:

1. Requester-initiator data blocks are defined.

The blocks describe **what** data is transferred over the PCI-X bus.

Requester-initiator behaviors are defined.

The behaviors describe how data transferred over the PCI-X bus is executed.

For the requester-initiator, up to 256 blocks of data transfers can be set up. In addition, **requester-initiator behaviors** are set up to specify how the requester-initiator intends to transfer the data blocks over the PCI-X bus.

If any target replies to a transfer and requests a split transaction, the data block attributes are moved internally to the split transaction map for further use. The transaction map can manage up to 32 split transactions. When completing split transactions, the **requester-target behaviors** are used to control the transfer.

The **completer-target behaviors** define how the target of the Agilent E2929A/B testcard acts. The completer-target can manage up to four split transaction queues.

To control the initiation of a split transaction completion, the **completer-initiator behaviors** are used.

The **transaction scheduler** decides whether the completer-initiator or the requester-initiator transaction is performed.

All data is supplied by the onboard **data memory** or from the onboard **real-time generator**.

The **real-time data compare** unit is used to compare data that is written to the memory against the actual memory content.

Data compare can also be performed on the data generator.

# **PCI-X Exerciser Configurations**

The configuration possibilities provided by the testcard and the GUI are basically the same as described for the testcard in the *Agilent E2929A/B PCI-X Getting Started Guide*.

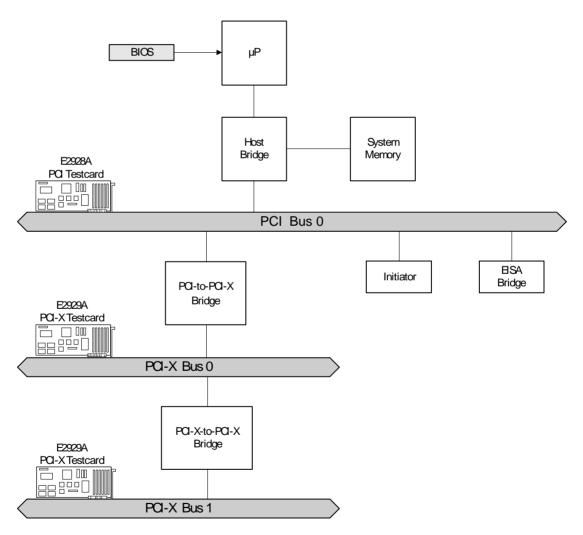

When using the Exerciser, your test requirements determine where to insert a testcard into the system under test. The following figure gives an overview of a typical computer system, where a single Agilent E2928A PCI testcard and two Agilent E2929A/B PCI-X testcards have been inserted.

You can use the Exerciser's initiator and target features to test each individual device—or the system as a whole:

• Testing devices

The testcard's requester-initiator can be used to initiate transactions to a target device under test. The testcard's target can be used to react to transactions initiated by the requester-initiator device under test. Initiator devices can also be bridges, for instance host bridges or PCI-X-to-PCI-X bridges.

The testcard can also be used for functional tests. For example, when testing communication devices (LAN cards, ATM cards), the testcard can be set up to generate and receive data blocks at specified data rates, thus allowing to test device and system behavior under full load.

• Testing a PCI-X-to-PCI-X bridge

To test the interfaces of a PCI-X-to-PCI-X bridge, testcards can communicate with other devices (or testcards) over a bridge or on the same bus. Thus, you can test whether the bridge forwards transactions to the correct bus.

During start-up, you can test whether configuration cycles are transferred correctly.

• Testing the whole system

When testing a system as a whole, the Exerciser can be used to:

- Set up any PCI-X traffic scenario quickly and in a repeatable way.

- Simulate PCI-X devices that are not yet available.

- Generate interrupts to test the system's interrupt processing capabilities.

## Setting Up a PCI-X Exerciser Test

Setting up a PCI-X Exerciser test includes the steps already described for the PCI-X standard analysis test (see *Agilent E2929A/B Getting Started Guide*).

Briefly, the following steps are necessary:

- 1. Inserting the testcard.

- 2. Connecting to the testcard.

- 3. Additionally, you have to set up the Exerciser as required for your test. This is described in detail in:

- "The PCI-X Exerciser as a Requester-Initiator Device" on page 53

- "The PCI-X Exerciser as a Completer-Target Device" on page 73

- "The PCI-X Exerciser as Completer-Initiator Device" on page 95

- "The PCI-X Exerciser as a Requester-Target Device" on page 101

- "Using Data Resources" on page 107

# **Typical PCI-X Transactions**

On every PCI-X system the different devices communicate via the PCI-X bus. This communication is controlled by the bus arbiter that determines which device may actively use the bus at any given time. This mechanism is used to avoid data collision and possible hardware damage. Basically, there are two different types of devices that operate on the bus: **initiators** (actors) and **targets** (reactors).

The Agilent E2929A/B PCI-X Exerciser testcard can simulate a requesterinitiator, a completer-target, a completer-initiator or a requester-target device or all together at the same time. This enables the testcard to emulate and/or test any device in your system under test.

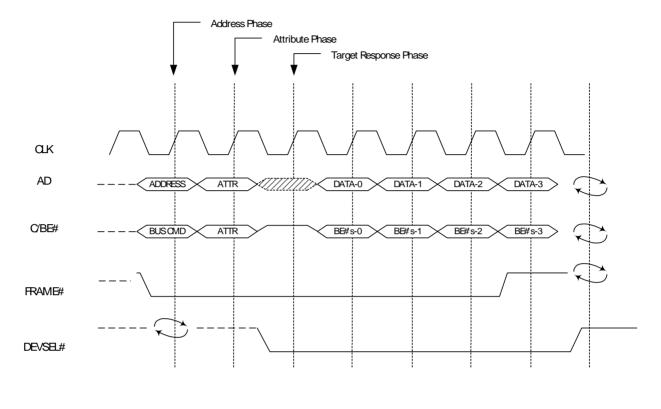

|                                          | The transfer of data between an initiator and a target device is performed<br>in one or more data transactions. These transactions are initiated and<br>controlled by the initiator, while the target reacts depending on the type<br>of transaction. |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transactions without Split<br>Completion | A successful transaction without split completion transaction includes the following steps:                                                                                                                                                           |

|                                          | 1. The requester-initiator requests bus access from the bus arbiter.                                                                                                                                                                                  |

|                                          | 2. The arbiter grants the requester-initiator to use the bus for a transaction.                                                                                                                                                                       |

|                                          | 3. The requester-initiator starts the transaction by sending the address of the completer-target, the bus command and the transaction attributes on the bus.                                                                                          |

|                                          | 4. The completer-target that owns the corresponding address range responds by asserting the DEVSEL# signal.                                                                                                                                           |

|                                          | 5. The requester-initiator initiates one or more data phases on the bus. If<br>the command was a write command, the requester-initiator also<br>sends the data. Otherwise, the data is sent by the completer-target.                                  |

|                                          | 6. On reaching the last data phase of the transaction, the requester-<br>initiator deasserts the FRAME# signal to indicate that it is ready to<br>complete the transaction.                                                                           |

| Transactions with Split Completion       | A successful transaction with a split completion transaction includes the following steps:                                                                                                                                                            |

|                                          | 1. The requester-initiator initiates the transaction by requesting access to the bus, asserting FRAME#, and driving the command and address on the bus.                                                                                               |

|                                          | 2. The completer-target terminates the transaction with a split response.                                                                                                                                                                             |

|                                          | 3. The data block properties are moved internally to a split transaction map, which is able to manage up to 32 open split transactions.                                                                                                               |

|                                          | 4. The completer-initiator initiates the split transaction completion, where Completer-Initiator behaviors are used.                                                                                                                                  |

|                                          | 5. The requester-target behaviors are used to terminate the split transactions.                                                                                                                                                                       |

# Running A Sample PCI-X Exerciser Session

The following application examples explain how the testcard can be used in various tests. After introducing the major scenarios for the PCI-X Exerciser and showing how to prepare for the sample sessions, you will be guided through the following examples:

- "Guided Tour: Generating Requester-Initiator Block Transfer" on page 23

- "Guided Tour: Specifying Requester-Initiator Behavior" on page 29

- "Guided Tour: Specifying Completer-Target Behavior" on page 34

- "Guided Tour: Defining the Transfers that will be given a Split Response" on page 40

- "Guided Tour: Specifying Completer-Initiator Behavior" on page 43

- "Guided Tour: Specifying Requester-Target Behavior" on page 46

# **Example Scenarios**

|                                      | The Agilent E2929A/B PCI-X Exerciser and Analyzer testcard can be<br>used for basically any test that might be required when developing<br>devices, chipsets, or drivers for the PCI-X environment. Here you can<br>find five examples that give a guided introduction to some of the main<br>features of the testcard and its Graphical User Interface (GUI).                                                                                                                                                                                                                               |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Testing a Completer-Target Device    | Let us say that you are integrating a PCI-X chip into an adapter or a system, or that your validation team (or even your customer) reports that your PCI-X chip or system is not working properly under certain circumstances. In both cases you will very likely need to generate or reproduce a given PCI-X scenario to find out how your chip behaves in a real environment. You may need to investigate for instance your chip's reaction to certain PCI-X commands or initiator protocol variations such as disconnect or sequence length, or to error conditions such as wrong parity. |

|                                      | In a case like this you can set up the Agilent PCI-X testcard as a requester-initiator to access your chip or system under test with certain commands or behaviors (stimuli from the testcard). This is explained in <i>"Guided Tour: Generating Requester-Initiator Block Transfer" on page 23.</i>                                                                                                                                                                                                                                                                                         |

| Testing a Requester-Initiator Device | If you are developing, debugging, validating, or characterizing a PCI-X<br>bus initiator device, you need a programmable target that can react<br>deterministically in the required fashion. The Agilent PCI-X Exerciser<br>provides this functionality. It has a 1-MB data memory that can be<br>accessed with either memory or I/O transactions. The target protocol<br>behavior is fully programmable for every transaction. This includes the<br>number of wait states, the termination type and so forth.                                                                               |

|                                      | An example, in which the Exerciser is set up as a completer-target, can<br>be found in "Guided Tour: Specifying Completer-Target Behavior" on<br>page 34.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

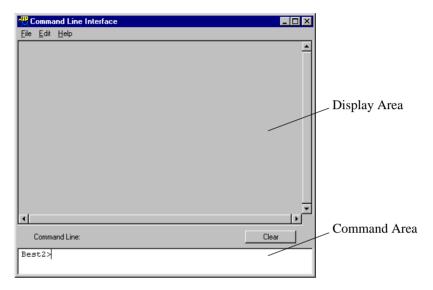

| Making C Function Calls Directly     | Besides the Graphical User Interface, the Agilent E2929A/B testcard also<br>features a C Application Programming Interface (option #320), providing<br>full access to all functions of the testcard.                                                                                                           |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | If you do not have the API installed or do not want to write complete C programs, you can use the Command Line Interface (CLI) instead, which is part of the GUI. With the CLI you can run scripts written in a simple script language.                                                                        |

|                                      | An example of how this is done is presented in "Guided Tour: Defining<br>the Transfers that will be given a Split Response" on page 40.                                                                                                                                                                        |

| Testing Split Transaction Completion | If a target replies to a transfer and requests a split transaction, the data<br>block attributes are moved internally to the split transaction map for<br>further use. The transaction map can manage up to 32 split transactions.                                                                             |

|                                      | The initiation of a split-transaction completion is controlled by the completer-initiator device. For setting up the testcard as a completer-initiator device, completer-initiator behaviors must be specified. This is explained in <i>"Guided Tour: Specifying Completer-Initiator Behavior"</i> on page 43. |

|                                      | When completing split transactions, the requester-target behaviors are used to control the transfer. Setting up the testcard as requester-target device is explained in <i>"Guided Tour: Specifying Requester-Target Behavior"</i> on page 46.                                                                 |

## **Preparing for the Exerciser Guided Tour**

The example described in the guided tour is designed to be performed in Offline/Demo Mode—without hardware.

All the setup files (\*.bst) and logic analyzer trace files (\*.wfm) that are mentioned in the following text can be found under <your\_installation\_directory>\samples\demo. If you did not change the default setting during installation, <your\_installation\_directory> will be c:\Program Files\Agilent\E2920 PCI-X Series. To prepare for the guided tour:

- 1 Launch the Agilent E2920 software.

- 2 From the Setup menu, choose Testcard Configuration.

- 3 In the Testcard Configuration window, select Offline/Demo Mode.

| Testcard Configuration                                                                                                                |                    |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| HW <u>C</u> onfig <u>H</u> elp                                                                                                        |                    |

| Ports           ○ PCI-X         Bus/Slot:         0x0000         PCI-X Browse           ○ RS232         COM 1         57600         ■ | OK<br>Cancel       |

| <ul> <li>C USB</li> <li>C Fast Host Interface</li> <li>O Iffline/Demo Mode</li> </ul>                                                 | Scan Ports<br>Ping |

| User Selected Testcard                                                                                                                |                    |

| E2929A Deep (64 Bit, 133 MHz)                                                                                                         |                    |

| Support / Licensing<br>✓ E2970A PCI-X Analyzer<br>✓ E2971A PCI-X Exerciser<br>✓ E2972A PCI-X Performance<br>Øffline/Demo mode: Us     |                    |

- Now choose E2929A Deep (64 bit, 133 MHz) from the User Selected Testcard list, and select all licenses in the Support/Licensing group.

Your display should look like the window shown above.

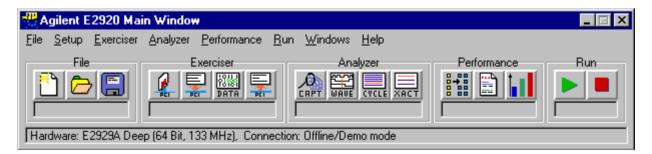

- **5** Click *OK* and the main window looks like this.

You are now ready to start the guided tours.

## Guided Tour: Generating Requester-Initiator Block Transfer

This example shows how to set up the testcard as a requester-initiator device that initiates data transfers on the PCI-X bus. More specifically, the following transfers are generated:

- A read of 10 bytes from data memory I/O space at address 0x10000d.

- A memory read of 273 bytes from data memory at address 0x10003000.

- A memory write of 18 bytes to the data generator. The lower address is 0x20000f0f, the upper is 0x30000000.

- A memory write of 130 bytes and 10 byte enables to the data memory at address 0x1000310d.

#### **Loading the Setup Files**

If you were connected to the testcard, the results of the test could be viewed on the screen. However, as you are working in offline mode, you need to start by loading the required files:

- 1 Load the setup file for this example (block\_transfer.bst) by selecting Load from the File menu in the main window.

- 2 Load the PCI-X signal waveform file for this example (block\_transfer.wfm) by selecting *Load from file* from the *File* menu in the Waveform Viewer window.

### **Setting up a Requester-Initiator Transaction**

Once you have loaded the setup file and the waveform file, continue by setting up the requester-initiator block for the test.

• Open the Requester-Initiator Block Editor dialog box by clicking the Transactions button in the main window or by selecting the *Transactions* item in the *Exerciser* menu.

In the Requester-Initiator Block Editor you see that the block transfers for this test are already displayed. They are stored in the setup file (block transfer.bst) together with all other settings.

| N 7 7          | quester Initiator Bl | ock Editor (E292 | 9A_DEEP - Offlin | e)       |         |           |   | _ 🗆 🗵   |

|----------------|----------------------|------------------|------------------|----------|---------|-----------|---|---------|

| <u>F</u> ile . | Help                 | AD32             | AD64             | NumBytes | IntAddr | Resource  |   | Add     |

|                |                      | - AD32           | AD04             | INUMBAGS | mexical | Thesource |   | Remove  |

| 0              | loRead               | 10000d\h         | 0\h              | a\h      | 0\h     | DataMem   |   | Tremove |

| 1              | MemReadBlock         | 10003000\h       | 0\h              | 111\h    | 0\h     | DataMem   |   |         |

| 2              | MemWriteBlock        | 20000f0f\h       | 30000000\h       | 12\h     | 0\h     | DataGen   |   |         |

| 3              | MemWrite             | 1000310d\h       | 0\h              | 82\h     | 0\h     | DataMem   |   |         |

|                |                      |                  |                  |          |         |           | Ţ |         |

|                | 1                    |                  |                  |          |         |           |   |         |

For reordering of blocks the testcard provides two queues into which each block can be transferred. You can transfer a block to queue A, to queue B or automatically to any free queue. Requester-initiator behaviors define which block from which queue is executed. This is shown in *"Guided Tour: Specifying Requester-Initiator Behavior" on page 29.*

In this example, block 0 is transferred to queue A. The other blocks are transferred automatically to any free queue.

### **Running the Test**

If you were connected to a testcard, you would start the test:

- by clicking the Run button 🕨 in the main window, or

- by choosing *Run* from the *Exerciser* menu.

#### **Viewing the Results**

Use the Analyzer's Waveform Viewer to inspect the test results. The waveforms were loaded from the waveform file block\_transfer.wfm.

1 Click the Waveform Viewer button in the main window (or use the *Waveform Lister* item in the Analyzer menu) to open the waveform viewer.

In the following window, you see a section of the waveform diagram in which the third transaction (memory write block to data generator) was executed.

| 👑 Waveform Viewer (E2929A_DE          | EP - Offline) [block transfer.wfm]                                               |

|---------------------------------------|----------------------------------------------------------------------------------|

| <u>File Run Time Signals M</u> arkers | Help                                                                             |

|                                       |                                                                                  |

|                                       |                                                                                  |

| Signal Val(A)                         | A, , , , , , , , , , , , , , , , , , ,                                           |

|                                       |                                                                                  |

| AD64 3000000\h                        | 30000000 FFFFFFF 00000000 0002417C 004801F4 0002417C 004801F4 00252CDC 007BF71C  |

| AD32 20000F0F\h                       | 30000000 21001812 00000000 0002417C 004801F0 0002417C 004801F0 00252CD8 007BF718 |

| CBE3_0 D\h                            |                                                                                  |

| CBE7_4 F\h                            | F                                                                                |

| FRAME                                 |                                                                                  |

| IRDY                                  |                                                                                  |

| TRDY                                  |                                                                                  |

| DEVSEL                                |                                                                                  |

| IDSEL                                 |                                                                                  |

| ri_act                                |                                                                                  |

| xact_cmd D\h                          | D F                                                                              |

| ri_done                               |                                                                                  |

|                                       |                                                                                  |

|                                       |                                                                                  |

| Marker A 100 📩 sa                     | 100 sa 0.75 sa/div. 111 sa                                                       |

| Marker B 107 🛨 sa                     |                                                                                  |

| A to B 7 sa                           | First Sample Range -10 to 200 sa Last Sample                                     |

At marker A the requester-initiator drives the dual address cycle command (coding 0xd) with the lower and upper address onto the bus. In the next cycle, it drives the memory write block command (coding 0xf) onto the bus.

It is also easy to identify that during this transaction:

- The requester-initiator is active (ri\_act is high).

- The AD32 signal first holds the target address (address phase) and then the transferred data in the four data phases (shown at marker B).

To see the corresponding section in the Bus Cycle Lister window:

2 Click the Bus Cycle Lister button in the main window (or use the *Bus Cycle Lister* item in the *Analyzer* menu) to open the bus cycle lister.

| Bus Cycle Lister (E2929A_DEEP - Offline) [block transfer.wfm]         File       Bun         Search       Help         Image: Search       Hel | _ 🗆 X    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 99: <idle></idle>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b></b>  |

| 100: Dual Addr Cycle LO Addr = 20000f0f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| 101: * Mem. Wt Blok HI Addr = 30000000 REQ64#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 102: Requester = BusO Device3 FuncO SeqID = 1 BC = 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| 103: <decoding> (no DEVSEL#, no IRDY#)</decoding>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 104: <response></response>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 105: <wait> (no TRDY#)</wait>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 106: <wait> (no TRDY#)</wait>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 107: Data = 0002417c 0002417c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 108: Data = 004801f4 004801f0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 109: Data = 00252cdc 00252cd8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 110: Data = 007bf71c 007bf718                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

| 111: <idle></idle>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>_</b> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •        |

To see the corresponding section in the Transaction Lister window:

**3** Click the Transaction Lister button in the main window (or use the *Transaction Lister* item in the *Analyzer* menu) to open the transaction lister.

| N.7.2 |                                          | EP - Offine) [block transfer.wfm]                                                          |

|-------|------------------------------------------|--------------------------------------------------------------------------------------------|

|       | ter <u>S</u> earch <u>H</u> elp<br>→T №3 | Goto:                                                                                      |

| 98:   | - Burst -                                | λ = 10003110 D = 3e457fbc 00a97310                                                         |

| 100:  | Mem. Wt Blck                             | Å = 30000000 20000f0f D = 00xxxxxx xxxxxxx WAIT = 4 Req. = (0,3,0) SeqID = 1 BC = 18       |

| 108:  | - Burst -                                | A = 30000000 20000f10 D = 004801f4 004801f0                                                |

| 109:  | - Burst -                                | A = 30000000 20000f18 D = 00252cdc 00252cd8                                                |

| 110:  | - Burst -                                | A = 30000000 20000f20 D = 007bf71c 007bf718                                                |

| 143:  | Memory Write                             | A = 1000310d D = xxb3xxxx xxxxxxx BE = 10111011 WAIT = 2 Req. = (0,3,0) SeqID = 2 BC = 130 |

| 148:  | - Burst -                                | A = 10003110 D = xxf4xx1a xxa2xx9a BE = 10101010                                           |

| 149:  | - Burst -                                | A = 10003118 D = xxa0xx65 xx4dxx9a BE = 10101010                                           |

| 150:  | - Burst -                                | A = 10003120 D = xx5exx5a xx48xxfa BE = 10101010                                           |

| 151:  | - Burst -                                | A = 10003128 D = xx06xx1f xxfaxx76 BE = 10101010                                           |

| 152:  | - Burst -                                | A = 10003130 D = xx72xx49 xx6fxx50 BE = 10101010                                           |

| 153:  | - Burst -                                | A = 10003138 D = xxaexxea xx1exxa2 BE = 10101010                                           |

| 154:  | - Burst -                                | A = 10003140 D = xxbcxxaa xx1cxx73 BE = 10101010                                           |

| 155:  | - Burst -                                | A = 10003148 D = xxbbxx2a xxfaxxe2 BE = 10101010                                           |

| 156:  | - Burst -                                | A = 10003150 D = xxb6xxea xx83xxff BE = 10101010                                           |

| 157:  | - Burst -                                | A = 10003158 D = xxf4xx53 xx1dxxdf BE = 10101010                                           |

| 158:  | - Burst -                                | A = 10003160 D = xx6dxx18 xx0fxx62 BE = 10101010                                           |

| 159:  | - Burst -                                | A = 10003168 D = xxdcxxad xxb4xx83 BE = 10101010                                           |

| 160:  | - Burst -                                | A = 10003170 D = xxaexx77 xxd2xxca BE = 10101010                                           |

| 161:  | - Burst -                                | A = 10003178 D = xx16xx4a xxe1xx18 BE = 10101010                                           |

| 162:  | - Burst -                                | A = 10003180 D = xxb2xxa8 xxfaxx3c BE = 10101010                                           |

| 163:  | - Burst -                                | A = 10003188 D = xx2fxx4c xx8exx37 BE = 10101010                                           |

|       |                                          |                                                                                            |

|       |                                          |                                                                                            |

The following table gives an overview of all of the traffic generated by the exerciser:

| Lines   | Transfer                    | Block Line |

|---------|-----------------------------|------------|

| 0       | I/O Read bytes 0 2          | 0          |

| 17      | I/O Read bytes 3 6          | 0          |

| 34      | I/O Read bytes 7 9          | 0          |

| 51 98   | Memory Read Block 273 bytes | 1          |

| 100 110 | Memory Write Block 18 bytes | 2          |

| 143 163 | Memory Write 130 bytes      | 3          |

In the transaction lister above, the last two transactions are displayed:

- Memory write block to data generator.

- Memory write to data memory.

Additionally, you can assign behaviors to each transaction block, which defines further protocol behaviors for the requester-initiator. These behaviors can be found in the Requester-Initiator Behavior Editor dialog box and are introduced in the following section.

# Guided Tour: Specifying Requester-Initiator Behavior

Whereas requester-initiator blocks describe **what** data is transferred over the PCI-X bus, requester-initiator behaviors describe **how** data is transferred over the PCI-X bus. In particular, behaviors control the partitioning of blocks into sequences and the reordering of blocks.

This guided tour gives an example of setting up the requester-initiator behaviors for the blocks specified in *"Guided Tour: Generating Requester-Initiator Block Transfer" on page 23*.

The properties of four behaviors are programmed as follows:

- Behavior 0

- The block is selected from queue A.

- The sequence length is 64 bytes.

- The sequence is broken into transactions at every second allowable disconnect boundary (ADB).

- The sequence is assigned tag 17.

- The number of steps is two.

- Behaviors 1 to 3

- The block is selected on a toggle basis from the queue that follows the last used queue.

- The sequence length is 64 bytes.

- For behavior 2, the sequence is broken into transactions at each ADB.

- The sequences for behaviors 1, 2 and 3 are assigned with an automatically selected free tag, tag 8 and tag 30 respectively.

The following table shows the summary of the specified behaviors:

| Behavior | Queue | Bytes | Disconnect             | Tag  | Steps |

|----------|-------|-------|------------------------|------|-------|

| 0        | А     | 64    | at every second<br>ADB | 17   | 2     |

| 1        | Next  | 64    | -                      | Auto | -     |

| 2        | Next  | 64    | at each ADB            | 8    | -     |

| 3        | Next  | 64    | -                      | 30   | -     |

For the remaining properties, the default values are used.

#### **Loading the Setup Files**

If you were connected to the testcard, the results of the test could be viewed on the screen. However, as you are working in offline mode, you need to start by loading the required files:

- 1 Load the setup file for this example (RIBehavior.bst) by selecting *Load* from the *File* menu in the main window.

- **2** Load the PCI-X signal waveform file for this example (RIBehavior.wfm) by selecting *Load from file* from the *File* menu in the Waveform Viewer window.

# Setting up the Requester-Initiator Behaviors

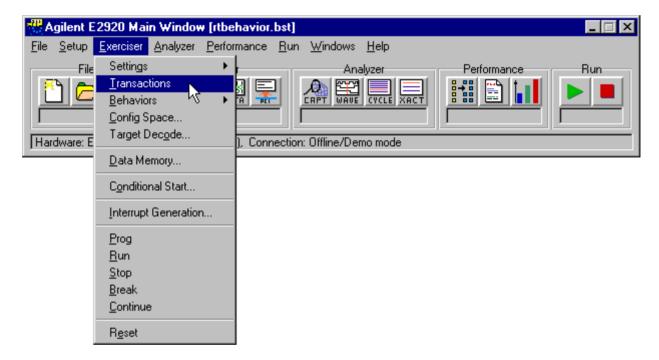

Once you have loaded the setup file and the waveform file, continue by setting up the requester-initiator behavior for the test.

♦ Open the Requester-Initiator Behavior Editor dialog box by selecting Exerciser -> Behaviors -> Requester Initiator.

| - Agilent E                | 2920 Main Window [ribe    | havior.bst]                                                                                                                                                    |                 |

|----------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <u>F</u> ile <u>S</u> etup | Exerciser Analyzer Perfor | mance <u>R</u> un <u>W</u> indows <u>H</u> elp                                                                                                                 |                 |

| Eile <u>S</u> etup<br>File | Settings                  | mance <u>R</u> un <u>W</u> indows <u>H</u> elp<br>Analyzer<br>Requester <u>Initiator</u><br>Completer I arget<br><u>Completer I arget</u><br>Requester T arget | Performance Run |

|                            | R <u>e</u> set            |                                                                                                                                                                |                 |

In the Requester-Initiator Behavior Editor you see that the behaviors for this test are already displayed. They are stored in the setup file (RIBehavior.bst) together with all the other settings.

| e <u>H</u> elp |       |           |            |       |       | <br>  |

|----------------|-------|-----------|------------|-------|-------|-------|

| Queue          | e Tag | ByteCount | Disconnect | Delay | Steps | Add   |

| l qa           | 17    | 40\h      | 2          | 1\h   | 2\h   | Remov |

| Next           | Auto  | 40\h      | No         | 1\h   | 0\h   |       |

| ? Next         | 8     | 40\h      | 1          | 1\h   | 0\h   |       |

| 3 Next         | 30    | 40\h      | No         | 1\h   | 0\h   |       |

|                |       |           |            |       |       |       |

### **Running the Test**

If you were connected to a testcard, you would start the test:

- by clicking the Run button 🕨 in the main window, or

- by choosing *Run* from the *Exerciser* menu.

#### **Viewing the Results**

Use the Analyzer's Transaction Lister to inspect the results of this test. The waveforms were loaded from the waveform file RIBehavior.wfm..

To open the transaction lister:

• Click the Transaction Lister button in the main window (or use the *Transaction Lister* item in the *Analyzer* menu).

| Transatio | DI Listor (E2020A DI            | EEP - Offline) (RIBehavior. wfm)                                                    |

|-----------|---------------------------------|-------------------------------------------------------------------------------------|

| 1000      | ter <u>S</u> earch <u>H</u> elp |                                                                                     |

|           |                                 | Goto:                                                                               |

| 37:       | - Burst -                       | λ = 10003038 D = cb3e8584 a2db208c                                                  |

| 39:       | I/O Read                        | A = 00100010 D = 2cdc7f82 BE = 0000 VAIT = 11 Req. = (0,3,0) SeqID = 8              |

| 56:       | Mem. Rd Blok                    | A = 10003040 D = af8cfbab ae8f054a WAIT = 11 Req. = (0,3,0) SeqID = 30 BC = 64      |

| 70:       | - Burst -                       | λ = 10003048 D = 909adb1f 8a1349b7                                                  |

| 71:       | - Burst -                       | A = 10003050 D = e203feaf ee12d794                                                  |

| 72:       | - Burst -                       | λ = 10003058 D = c99eeaa0 48e312fc                                                  |

| 73:       | - Burst -                       | A = 10003060 D = abd22efb 2ea706ca                                                  |

| 74:       | - Burst -                       | A = 10003068 D = 4402bcff bc2ec0ba                                                  |

| 75:       | - Burst -                       | λ = 10003070 D = a3aa6d39 ca8e4aaa                                                  |

| 76:       | - Burst -                       | A = 10003078 D = a2a9fe0d 2fe7d082                                                  |

| 80:       | I/O Read                        | A = 00100014 D = xxdacfe0 BE = 1000 WAIT = 11 Req. = (0,3,0) SeqID = 17             |

| 97:       | Mem. Rd Blck                    | A = 10003080 D = 566ad0b9 a9398410 WAIT = 11 Req. = (0,3,0) SeqID = 0 BC = 64       |

| 111:      | - Burst -                       | A = 10003088 D = 72922558 23c3f70c                                                  |

| 112:      | - Burst -                       | λ = 10003090 D = e2ea8adf 356bb4ea                                                  |